#

#### IMPLEMENTING A LEADING LOADS PERFORMANCE PREDICTOR ON COMMODITY PROCESSORS

BO SU<sup>†</sup> JOSEPH L. GREATHOUSE<sup>‡</sup> JUNLI GU<sup>‡</sup> MICHAEL BOYER<sup>‡</sup> LI SHEN<sup>†</sup> ZHIYING WANG<sup>†</sup>

> <sup>†</sup>NUDT <sup>‡</sup>AMD RESEARCH JUNE 19, 2014

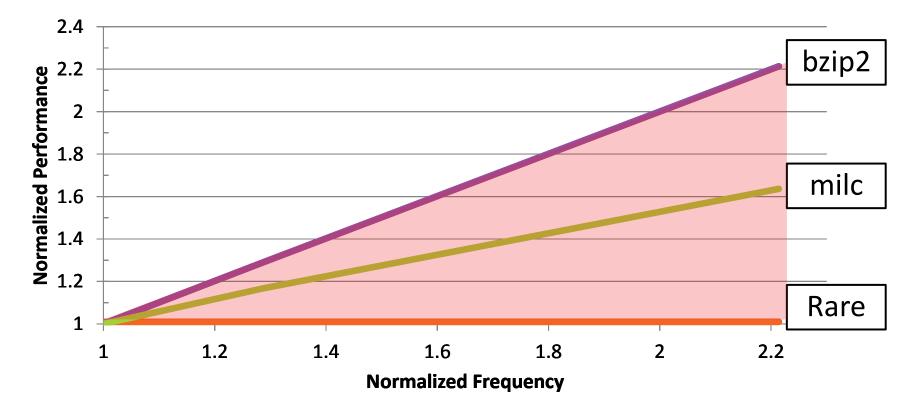

# How fast is your application at different CPU frequencies?

2 | IMPLEMENTING A LEADING LOADS PERFORMANCE PREDICTOR ON COMMODITY PROCESSORS | JUNE 19, 2014

#### WHAT HAPPENS WHEN YOU CHANGE FREQUENCY? **AMD**

3 | IMPLEMENTING A LEADING LOADS PERFORMANCE PREDICTOR ON COMMODITY PROCESSORS | JUNE 19, 2014

#### WHY DON'T NAÏVE ESTIMATES ALWAYS WORK?

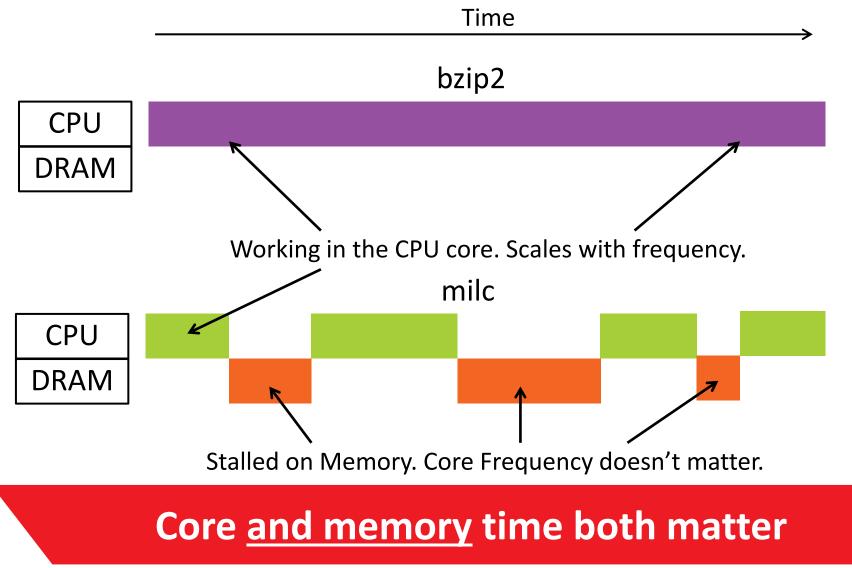

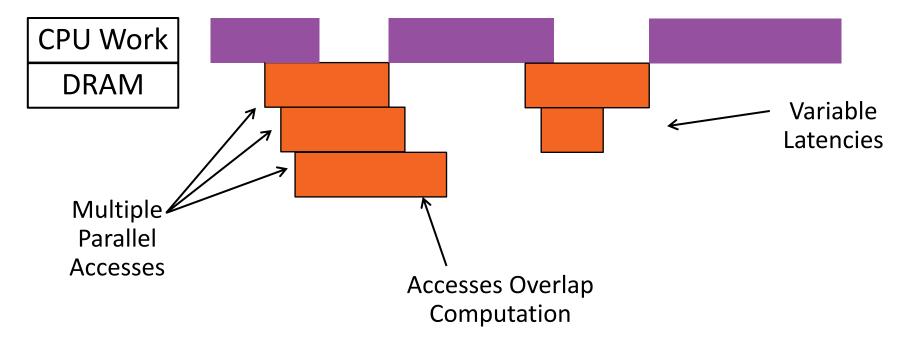

#### HOW DO YOU ESTIMATE "MEMORY TIME"? MODERN CORES MAKE THIS DIFFICULT

#### Count the amount of time with an outstanding load?

Count last-level cache misses?

Described by 3 separate groups in CF 2010, IEEE TOC, and IGCC 2011

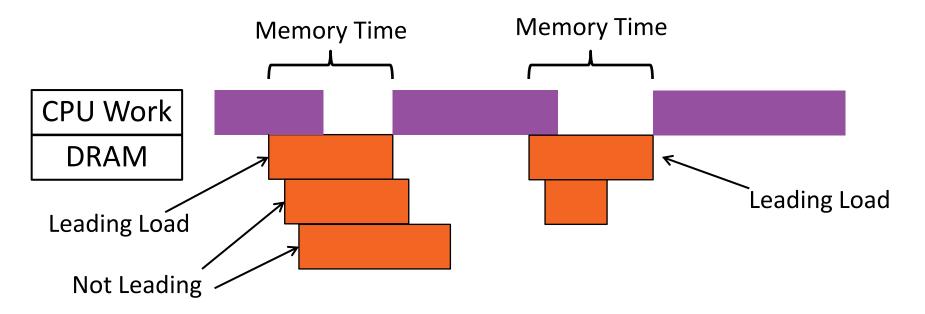

Memory time approximately time that a leading loads is active

<u>Simulation</u>: ~0.2% estimation error across 2x change in frequency

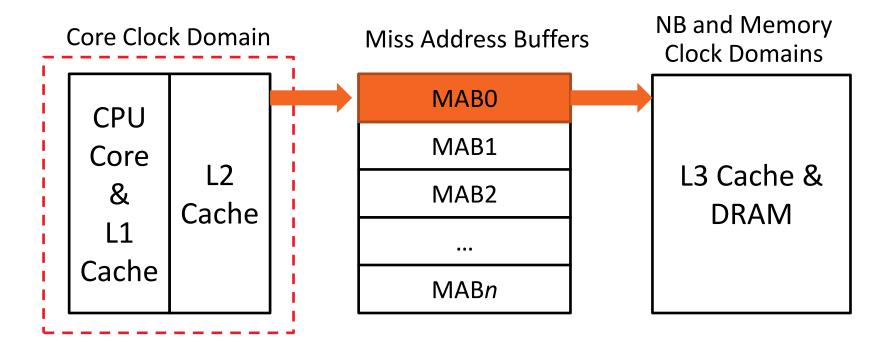

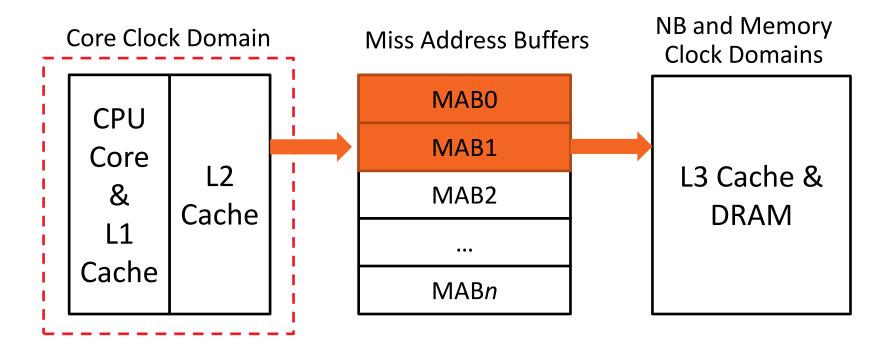

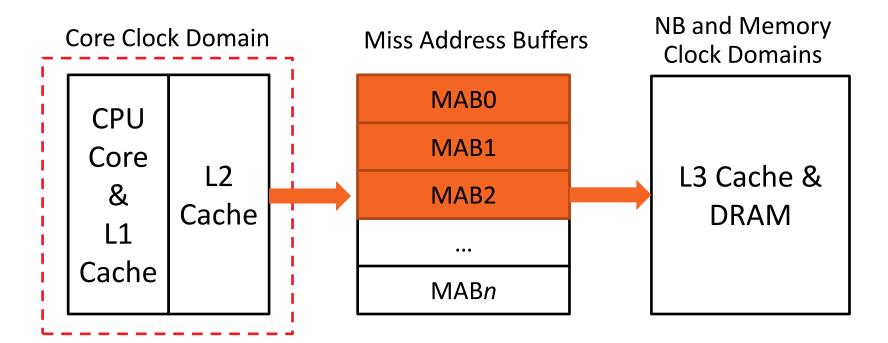

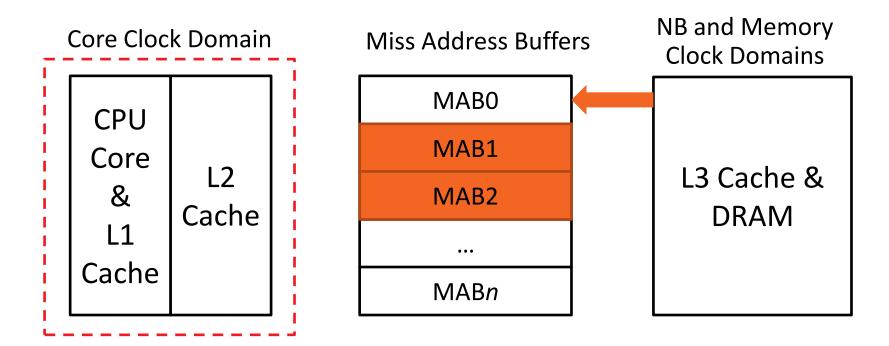

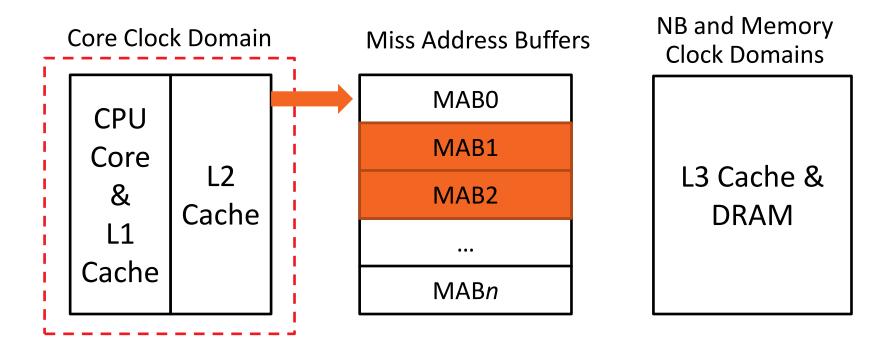

#### L2 cache misses held in Miss Address Buffer (MAB)

- MAB entries have a static priority (e.g. MABO is highest priority)

- Highest priority empty MAB holds the miss until it returns from memory

#### L2 cache misses held in Miss Address Buffer (MAB)

- MAB entries have a static priority (e.g. MABO is highest priority)

- Highest priority empty MAB holds the miss until it returns from memory

#### L2 cache misses held in Miss Address Buffer (MAB)

- MAB entries have a static priority (e.g. MABO is highest priority)

- Highest priority empty MAB holds the miss until it returns from memory

#### L2 cache misses held in Miss Address Buffer (MAB)

- MAB entries have a static priority (e.g. MABO is highest priority)

- Highest priority empty MAB holds the miss until it returns from memory

#### L2 cache misses held in Miss Address Buffer (MAB)

- MAB entries have a static priority (e.g. MABO is highest priority)

- Highest priority empty MAB holds the miss until it returns from memory

Measure occupancy time of the highest-priority MAB

- HW event 1: CPU Clocks not Halted (for Execution Time)

– Performance Event 0x76

- HW event 2: MAB Wait Cycles (for Memory Time)

- Performance Event 0x69

– Family 15h Processors: Unit Mask 0

Memory Time(f1) = MAB Wait Cycles(f1)/(f1)

Core Time(f1) = Execution Time(f1)-Memory Time(f1)

Execution Time(f2) = Core Time(f1) \* f1/f2 + Memory Time(f1)

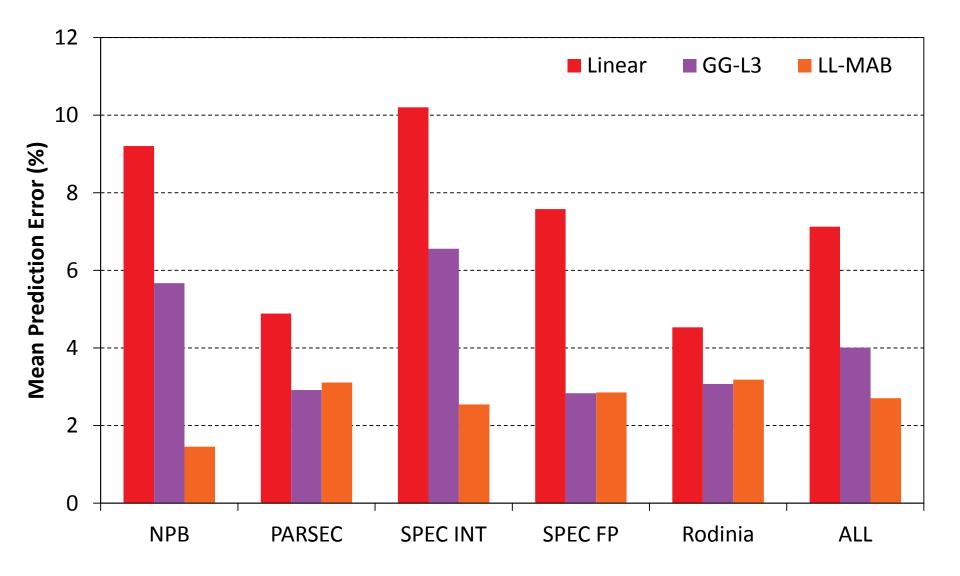

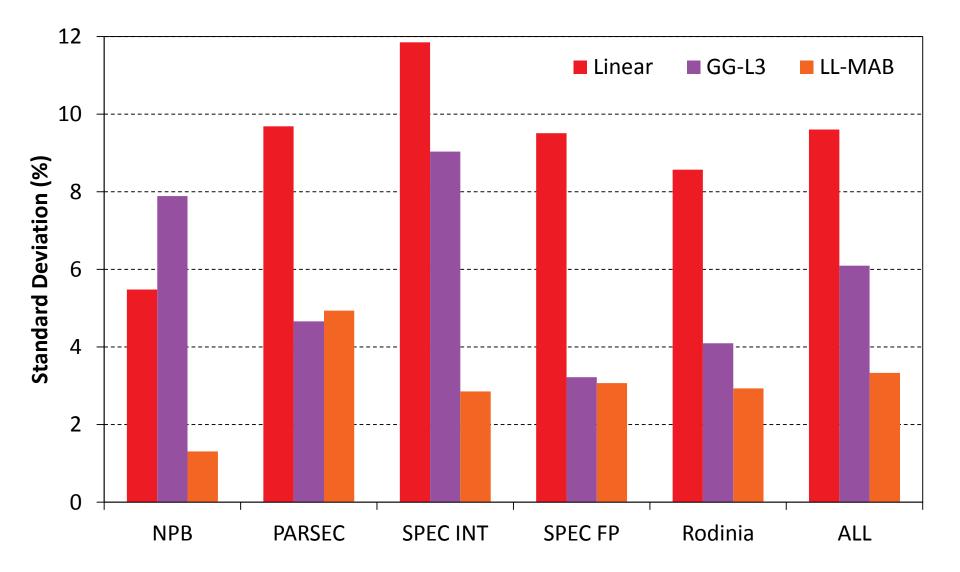

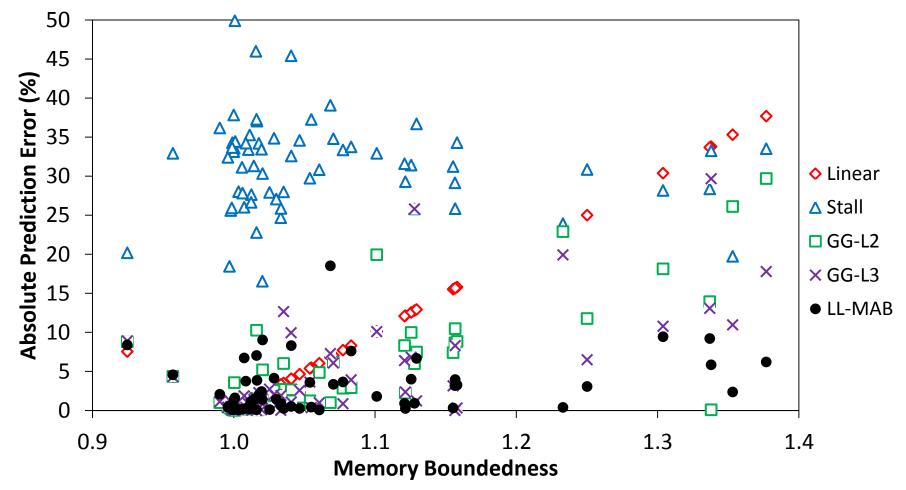

#### **EVALUATING PERFORMANCE PREDICTORS**

- Run benchmarks at frequency 1, estimate runtime at frequency 2

- Run benchmark at frequency 2.

- Difference between observed and estimated is estimation error.

- Estimation mechanisms:

- Linear: Performance scales exactly with frequency (like bzip2)

- Green Governor:

- Count L3 cache misses

- Assign delay to each cache miss

- # Cache Misses \* delay = "memory time"

- LL-MAB: Count MAB0 cycles at "memory time"

#### **EXPERIMENTAL SETUP** OTHER PROCESSORS TESTED IN THE PAPER

#### AMD Opteron<sup>™</sup> 4386 Processor

- 2<sup>nd</sup> Generation Family 15h "Piledriver" CPU

- Minimum Frequency: 1.4 GHz, Maximum non-boost frequency: 3.1 GHz

#### Fedora<sup>®</sup> 19 Desktop (kernel version 3.10.6-200)

- Locked benchmarks to single core with *numactl*

- Used *msr-tools* to read performance counters around benchmark runs.

- CPUFreq userspace governor to manually control DVFS state. Boosting disabled.

#### 66 Single-threaded benchmarks from:

- SPEC<sup>®</sup> CPU 2006

- NAS Parallel Benchmarks

- PARSEC

- Rodinia

### MEASURE AT 3.1 GHZ, ESTIMATE 1.4 GHZ RUNTIME **AMD**

## STANDARD DEVIATION IS IMPORTANT FOR PREDICTIONS AMD

#### **DISCLAIMER & ATTRIBUTION**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **ATTRIBUTION**

© 2014 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Other names are for informational purposes only and may be trademarks of their respective owners.

# Backup Slides∡

#### PREDICTION ACCURACY PER BENCHMARK

Memory Boundedness = Ratio of execution cycles at two frequencies

- 1.0 = no change in cycles (completely compute bound, e.g. bzip2)

<sup>19 |</sup> IMPLEMENTING A LEADING LOADS PERFORMANCE PREDICTOR ON COMMODITY PROCESSORS | JUNE 19, 2014

#### CONCLUSION

First leading loads implementation on real processors

- ▲ Higher accuracy than existing predictors

- ▲ Lower accuracy than simulation due to HW complexity

- Lightweight estimation mechanism (only requires 2 counters)

Path to better performance and power prediction